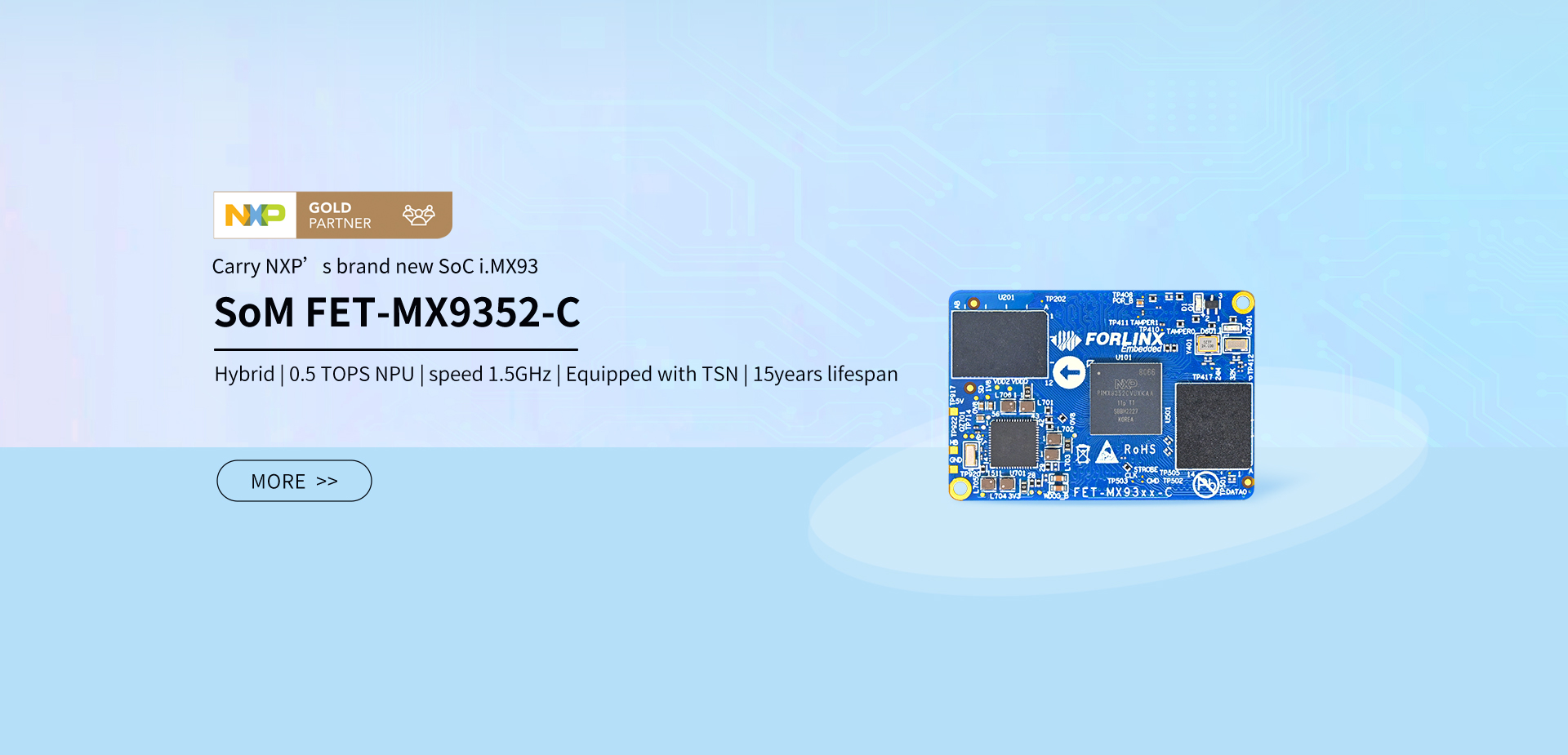

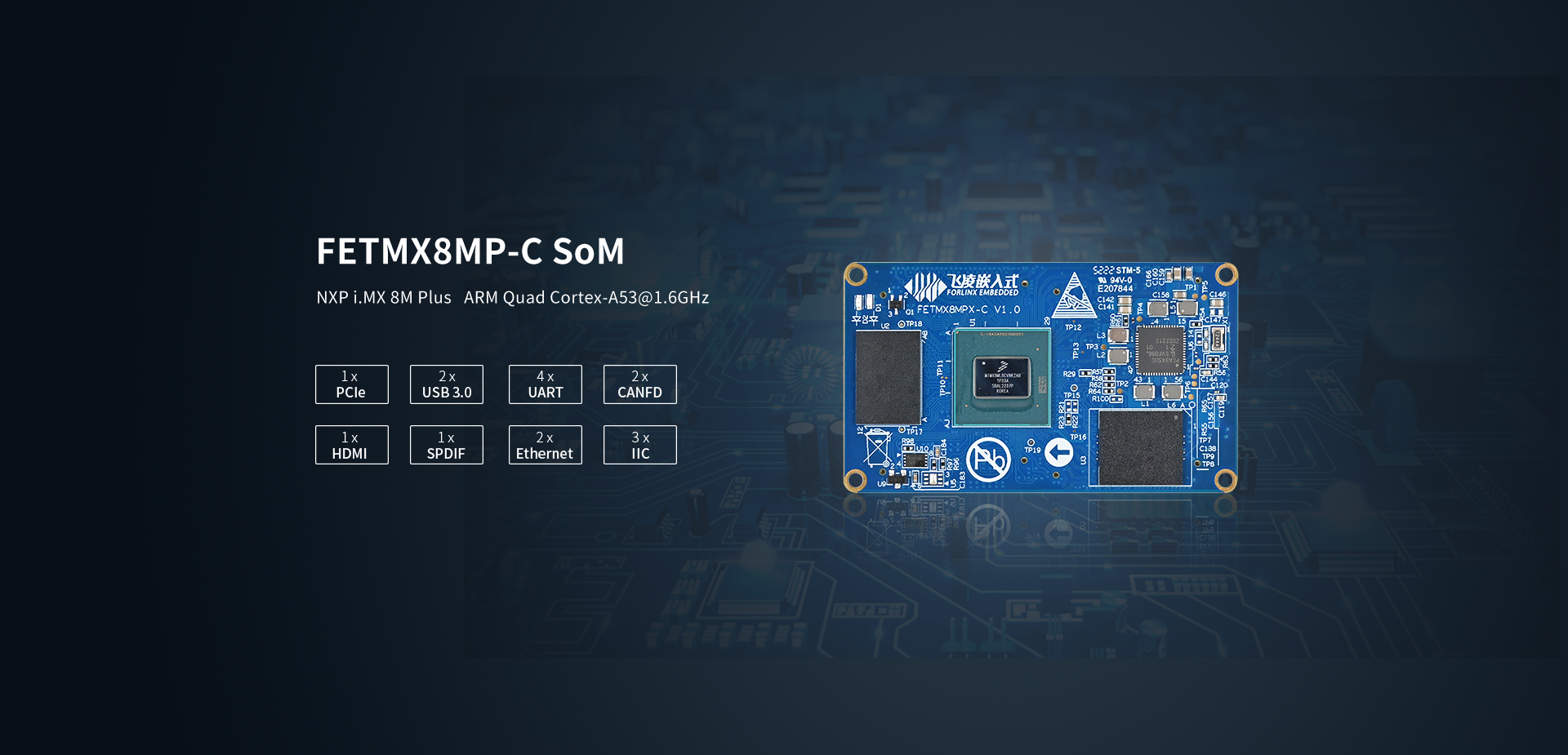

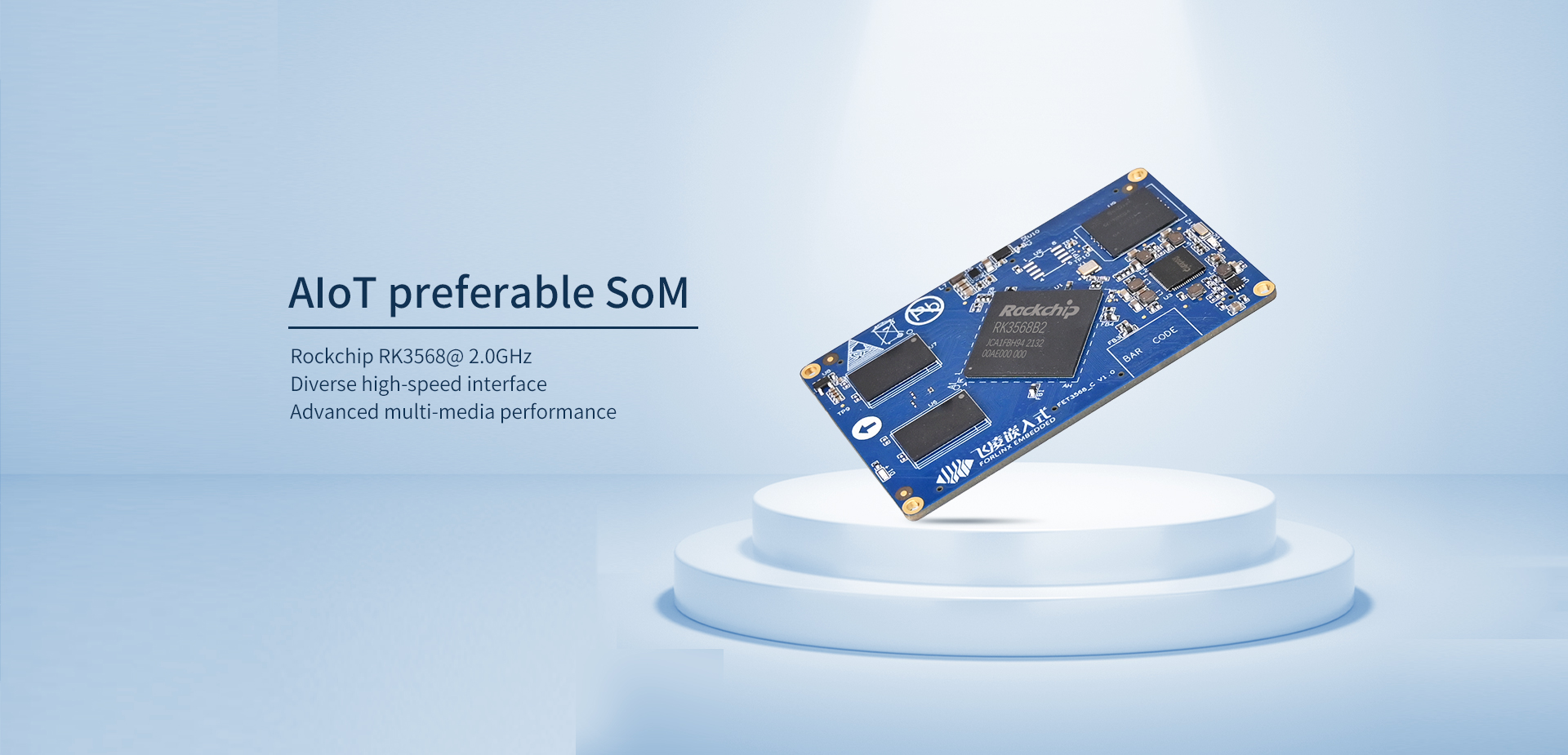

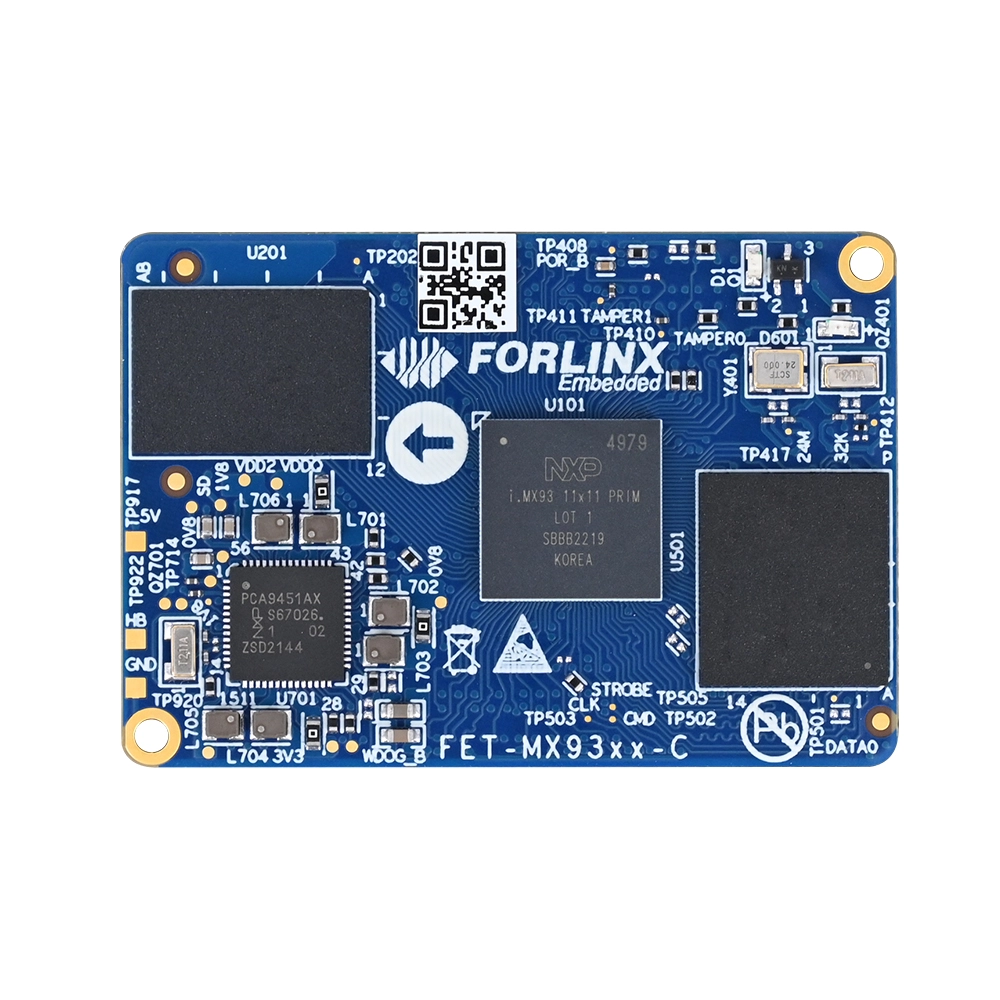

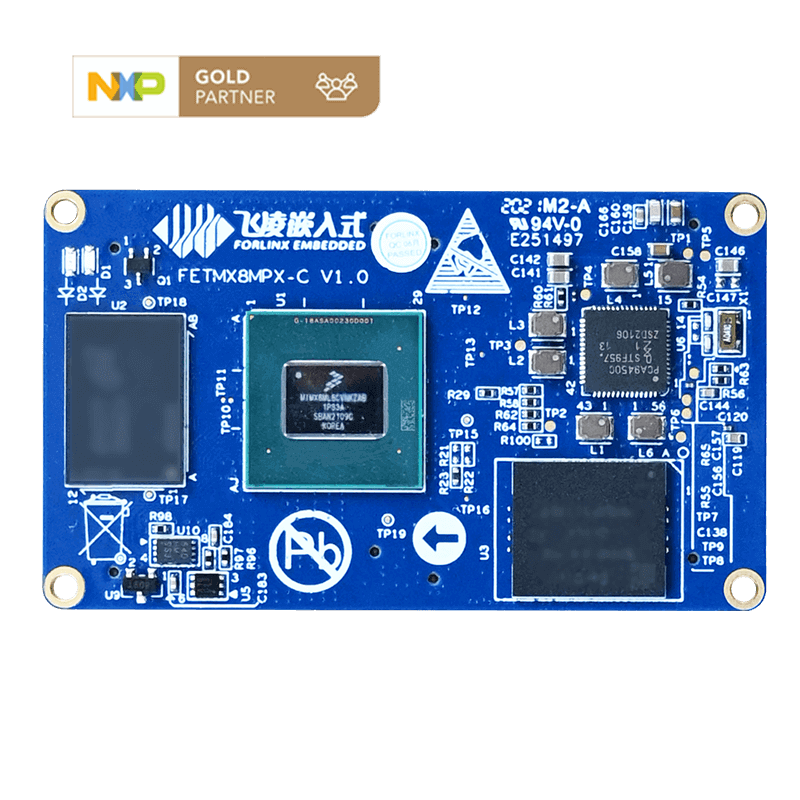

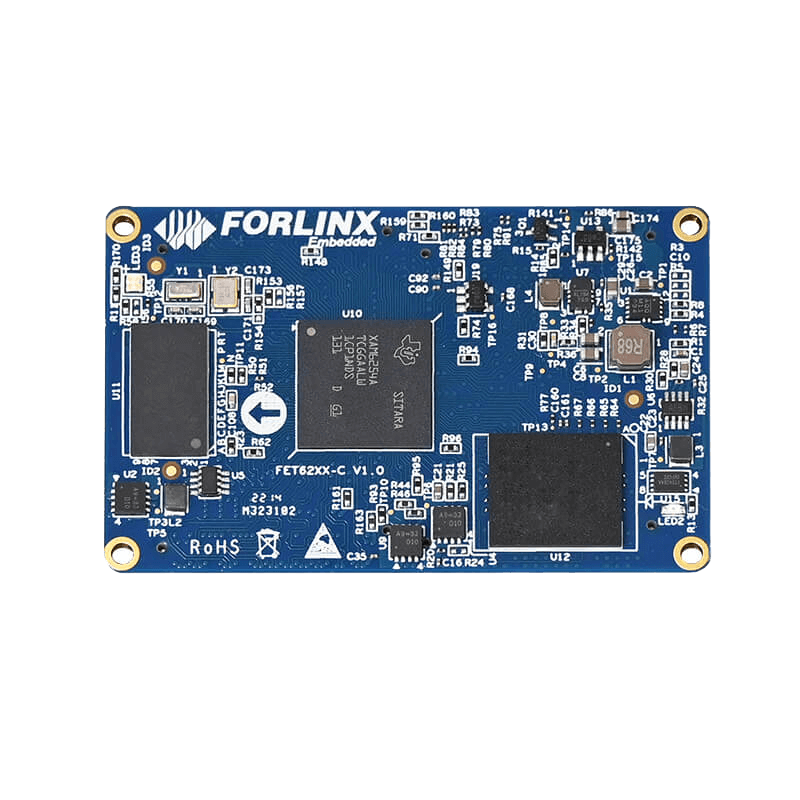

Featured Products

About us

- 17

years

History

- 30K

+

Enterprise Users

- 80K

+

Engineer Users

- 45

%

R&D Personnel

- 13K

㎡

Office Park

Why Forlinx?

-

Robust Quality

Our products are designed to run 24/7 in critical applications and to withstand harsh environments. -

Platform Scalability

Scalability ensures seamless migration of an embedded platform to future technology without the need for a redesign. -

Direct Engineer Support

Technical support is provided directly by Forlinx product design engineers streamlining customers' design flow. -

10-year Availability

Forlinx guarantees 10 years of product availability. The product life-cycle is extended with well-established last-time-buy and component stocking programs. -

In-house Manufacturing

Forlinx products are made in-house in ISO9001:

2015-certified facilities for high-quality and flexible logistics. -

Comprehensive Documentation

Forlinx supports its products with detailed technical reference manuals, carrier-board designs packages and schematics.

首页新闻

公司动态

- Advance Hand in Hand | Forlinx Authorized as NXP Gold Partner 2021-01-07

- International Event | Forlinx Embedded Makes Grand Appearance at Embedded World 2024, Nuremberg, Germany 2024-04-11

- Forlinx Embedded to Showcase at 2024 Embedded World Exhibition in Nuremberg, Germany 2024-03-30

- A Team From NXP Visited the Headquarters of Forlinx Embedded 2024-01-05

- Forlinx Embedded Launches FET-D9360-C SoM Based on D9-Pro High-Performance Industrial Processor 2023-12-26

- Texas Instruments (TI) Technical Team Visits Forlinx Embedded Headquarter 2023-12-22

行业动态

- Pressure Displacement Profile Analyzer Solution Based on FETMX8MM-C SoM 2024-04-23

- Forlinx Embedded AM62x SoM, Empowering a New Generation of HMI 2024-04-18

- Steps for Reading and Modifying U-Boot Environment Variables at the Kernel Stage 2024-04-16

- Display and Modification of LVDS Display Interface on AM62x Development Board 2024-04-08

- With AMP Dual System Support, RK3568 SoM Boosts Real-Time Performance 2024-04-02

- Introduction to SPI Communication in the TI AM62x Processor 2024-03-28