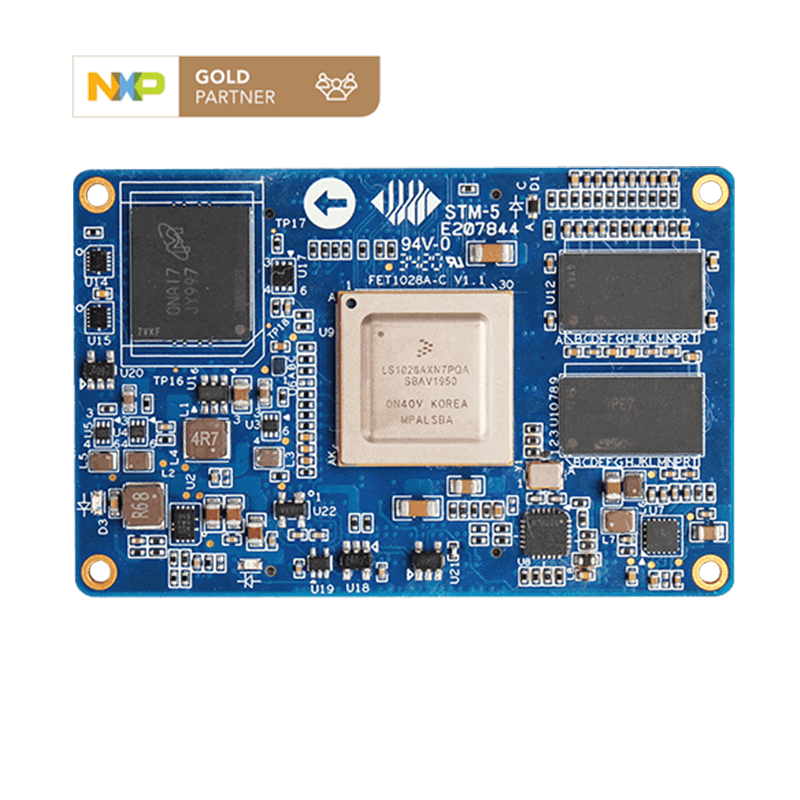

GPIO Multiplexed and Ethernet Subnet based on LS1028A Development Board

Multiplex GPIO

Here we take SPI multiplexed to GPIO for demonstration

From LS1028A datasheet we can know that SPI_SIN could be multiplexed to GPIO_DAT13, SPI3_SCK could be multiplexed to GPIO3_DAT14, SPI_SIN could be multiplexed to GPIO3_DAT13 and SPI3_SOUT could be multiplexed to GPIO3_DAT16

And we can also know that the RXW is SPI3_PMUX

From the sheet we can know that when SPI3_PMUX=1, the pin is configured to GPIO3_DAT[16:13], we just need change its RCW, then recompile and flash it to board.

RCW path:

OK1028-linux-fs/packages/firmware/rcw/ls1028ardb/R_SQPP_0x85bb/rcw_1500_gpu600.rcw

Verify on board

root@forlinx:~#ls /sys/class/gpio

export gpiochip416 gpiochip448 gpiochip480 unexport

execute the above command and we'll get four couples of gpiochip as below

Gpiochip480 for gpio1[];

Gpiochip448 for gpio2[];

Gpiochip416 for gpio3[];

users can refer to this to verify their target pin by GPIO3_DATx=gpiochip416+x,

here we take GPIO3_DAT14 for demonstration

root@forlinx:~#echo 430 > /sys/class/gpio/export

root@forlinx:~#echo out > /sys/class/gpio/gpio430/direction

root@forlinx:~#echo 1 > /sys/class/gpio/gpio430/value

root@forlinx:~#cat /sys/class/gpio/gpio430/value

1

root@forlinx:~#echo 0 > /sys/class/gpio/gpio430/value

root@forlinx:~#cat /sys/class/gpio/gpio430/value

0

voltage will be changed accordingly.SPI3 will be multiplexed to GPIO completely, when SPI3_PMUX=1, the pin will be configured to GPIO3_DAT[16:13]

Ethernet on OK1028A-C

eno0 is SGMII1G-T protocol, and swp0-swp3 is QSGMII1G

About Switch

Ethernet system consists of ENETC and TSN enabled switch

ENETC is a virtical Ethernet controller with GbE and TSN enabled. ENETC provides fully integrated GbE MACs. It can support IP, TCP, UDP and ICMP.

The ENETC features

- •Implements the full 802.3 specification withpreamble/SFD generation, frame padding generation, CRC generation andchecking.

- •One 10/100/1000/2500 Mbit/s Ethernet port. ThroughSerDes, SGMII (1G/2.5G) and USXGMII (2.5G) MAC-PHY

- specificationsare supported.

- •One 10/100/1000 Mbit/s Ethernet port with RGMIIinterface.

- •One 2500 Mbit/s Ethernet port connected internallyto TSN Switch for switch data transmission.

- •One 1000-Mbit/s Ethernet port connected internallyto TSN Switch for switch management.

- •Supports jumbo Ethernet frames with a size up to9600 bytes

- •Supports double tagged VLAN frames according toIEEE 802.1Q

- •Supports IEEE 802.1Qbu preemption

- •PCI Express root complex integrated endpointdevice

LS1028A development board features

- •Four external 10/100/1000/2500-Mbit/s Ethernetports. Through SerDes, SGMII (1G/2.5G) and USXGMII (2.5G) MAC

- PHYspecifications are supported.

- •One 2500 Mbit/s Ethernet port connected internallyto ENETC for data transmission.

- •One 1000 Mbit/s Ethernet port connected internallyto ENETC for management.

- •One internal CPU port, for frame extraction andinjection.

- •128KB of integrated shared packet memory.

- •Fully nonblocking wire-speed switching performancewith weighted random early detection (WRED) for all frame sizes.