How to Work with GPMC on OK5718-C Development Board?

1. Overview

GPMC is short for General-Purpose Memory Controller and it is a kind of interface to be used for AM5718 processor to communicate with NOR Flash, NAND Flash, SRAM and other external storage devices. It has below features

1) flexible 8-bit and 16-bit async storage interface

2) up to 8 chip selections

3) can support NAND and NOR Flash, NOR Flash is multiplexed with SRAM

4) support contigious visiting to off-chip memory up to 512MB

2. Hardware connection of GPMC

1) CPMC connected with 16-bit external memory device with address/data multiplexed.

2) GPMC connected with 16-bit non-multiplxed external memory device

3) GPMC connected with 8-bit non-multiplexed memory device

4) GPMC connected with 8-bit NAND Flash

3. GPMC on OK5718-C

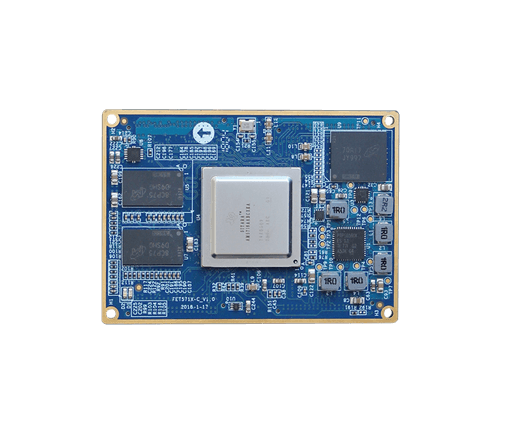

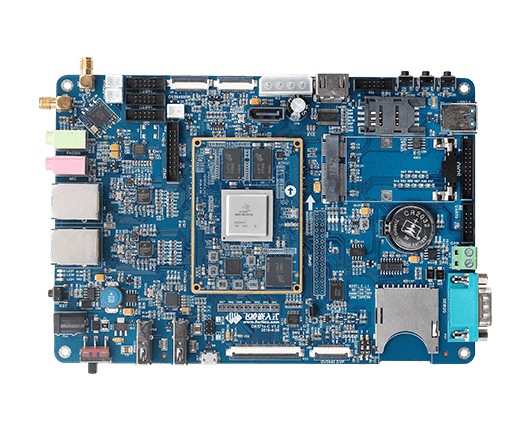

OK5718-C is preserved with GPMC interface. GPMC_AD[15: 0] is a multiplexed signal of data/ address, and it could be used for GPMC device testing. Pin definition is as below

in this demo, GPMC on OK5718-C is configured as async mode and also NOR Flash is multiplxed with address / data, actually, only below I/O used

GPMC_AD[15:0]: 16-bit address/ data

GPMC_CS0/ GPMC_CS3: chip select

GPMC_OEN_REN: output enable

GPMC_WEN: writing enable

GPMC_ADVN_ALE:address valid

4. Device tree configuring

GPMC related description in Linux kernel please refer to below files:

OK57xx-linux-kernel/Documentation/devicetree/bindings/memory-controllers/omap-gpmc.txt

OK57xx-linux-kernel/Documentation/devicetree/bindings/mtd/gpmc-nor.txt

OK57xx-linux-kernel/Documentation/devicetree/bindings/mtd/gpmc-nand.txt

device tree needed to be modified is OK57xx-linux-kernel/arch/arm/boot/dts/ok5718-idk.dts

below is configured device tree code

1) GPMC pin configuring

2) add GPMC node

configure chip select pin as 3. Base address to 0x8000000 and address space to 0x1000000

ranges =;

the configured timing sequence

5. Testing

Cross-compile the testing program code and copy app-fram to OK5718-C development board

execute app-fram read command

captured CS3 ADVN and En wave are as below, read and writing cycle of GPMC is 112ns

channel 1 is chip selection CS3, channel 2 is output enable signal OEn

channel 1 is chip selection advn, channel 2 is output enable signal OEn

channel 1 is chip selection advn, channel 2 is output enable AD2 signal