LCD Porting Based On i.MX6 Series 3.0.35 Kernel

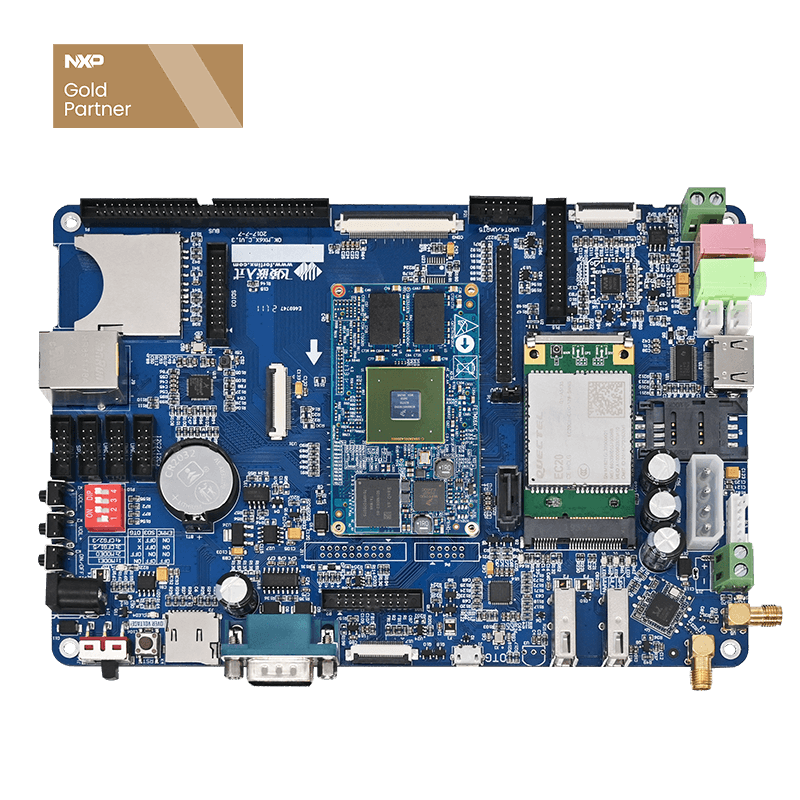

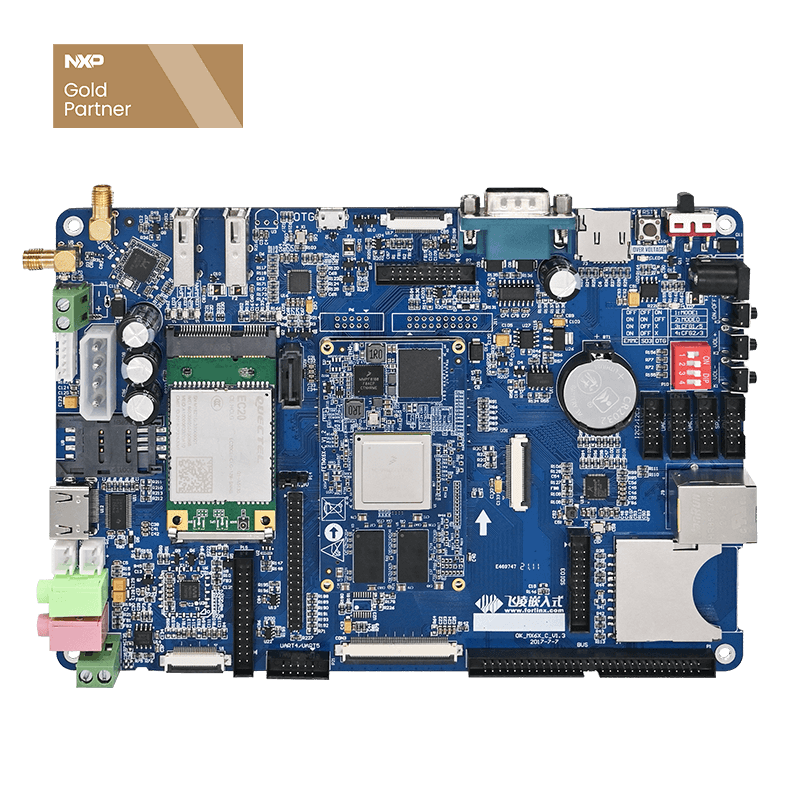

The main platform used in this article is iMX6 Series, linux3.0.35 operating system. The reference user information is OKMX6Q-C, OKMX6DL-C (Linux) user information.

When debugging whether the LCD screen can be used on the development board, we should first check if the line sequence used on the screen hardware can be consistent with the hardware line sequence on the development board; software debugging can only be performed if the hardware can be connected to the development board. Then, after the hardware is connected, check whether the LCD screen is lit. If the screen cannot be lit, first check the PWM backlight control; when the screen can be lit, we can debug the display, which is the main purpose of this article.

Let's take the debugging of the 10.4-inch LCD screen display as an example, and briefly talk about the main modifications that need to be made in the software during LCD debugging.

1. Modification of uboot part

Regarding the modification of the UBOOT part, the main function is to display the boot logo normally and pass the parameter information required by the kernel to the kernel. UBOOT modification mainly involves the following two files:

❶ Modify the display parameters in uboot-2009-08/include/configs/mx6q_sabresd.h, as shown in the red box in the following two pictures

❷ Modify the board/freescale/mx6q_sabresd/mx6q_sabresd.c file system and add the parameters displayed by the LCD: the red part is the added item.

static struct fb_videomode displays[] = {

{

.name = "AT104-WVGA",

.refresh = 60,

.xres = 800,

.yres = 600,

.pixclock = 25000,

.left_margin = 210,

.right_margin = 40,

.upper_margin = 23,

.lower_margin = 3,

.hsync_len = 6,

.vsync_len =2,

.sync = FB_SYNC_CLK_LAT_FALL,

.vmode = FB_VMODE_NONINTERLACED,

.flag = 0,

.mode = FB_VIDEOMODE_LCD,

}

2. Modification of relevant parts of the kernel

The LCD configuration of the kernel part is the normal display of the LCD screen after the system is started. Just modify one file.

Modify linux-3.0.35/drivers/video/mxc/mxc_lcdif.c and add the red part to the following structure. The parameters in the red part are the same as those in UBOOT.

static struct fb_videomode lcdif_modedb[] = {

………………….

/* 800x480 @ 60 Hz , pixel clk @ 33.3MHz */

"AT070-WVGA", 60, 800, 480, 30030, 210, 46, 22, 23, 10, 10,

FB_SYNC_CLK_LAT_FALL,

FB_VMODE_NONINTERLACED,

0,},

…………………………………….

{

"AT104-WVGA", 60, 800, 600, 25000, 210,40, 23, 3, 6, 2,

FB_SYNC_CLK_LAT_FALL,

FB_VMODE_NONINTERLACED,

0,},

}

Pay attention:

The name AT104-WVGA needs to be consistent with the settings in UBOOT and the kernel. There is no limit to the name. The only requirement is that UBOOT and the kernel must be consistent.

The modifications that we often involve in the LCD display part are mainly the parts mentioned above. After the modification, write the image file generated by recompilation to the development board, and connect it to the 10.4-inch LCD screen to see it. The screen can be displayed normally.

3. Understanding of relevant parameters

Some customers may not know much about the setting of the LCD parameter values involved. Here is a brief explanation of my own understanding:

First look at the definition of fb_videomode in the include/linux/fb.h file of the kernel:

The parameters defined above also correspond to those in UBOOT. These values are determined by the manual provided by the LCD manufacturer.

Next, let's take a 10.4-inch screen as an example to see the parameters in the screen manual

The 28 in the red box in the figure refers to the typical value of vertical Blanking, and the 256 in the red box refers to the typical value of Horizontal Blanking.

Below is a block diagram showing the relationship of these parameters:

From the above schematic diagram, we can know that in the screen manual of the 10.4-inch screen

Left_margin+right_margin+hsync_len=256

Upper_margin+lower_margin+vsync_len=28

When setting left_margin, right_margin, and hsync_len, make sure that their sum is 256.

When setting upper_margin, lower_margin, and vsync_len, make sure that their sum is 28.

Some LCD manuals will directly give the values of these 6 parameters, then you can set them directly according to the values given in the hardware manual, and fine-tune them when debugging.

How to determine the pxclock parameters:

dotclock=1/dotclock, where dotclock can choose the typical value of 40MHz in the manual, then calculate pixclock=25000 picoseconds

Actual refresh rate=40000000Hz÷((Left_margin+right_margin+hsync_len+xres)*(Upper_margin+lower_margin+vsync_len+yres))≈60Hz

After we burn the modified image to the development board, we can see the actual parameters of the screen settings through the fbset command as shown below:

These reference values provided in the manual can be fine-tuned according to the actual usage.

A simple table to clarify the meaning of each member of fb_videomode:

| Name | Manual Abbreviation | Meaning |

| name | No | LCD screen name (optional) |

| refresh | No | Refresh rate (usually 60Hz) |

| xres | No | number of pixels per line |

| yres | No | number of lines on the screen |

| pixclock | No | The length of each pixel clock cycle in picoseconds (10 to the minus 12th of a second) |

| left_margin | HBP (Horizontal Back Porch) | The number of pixel clock cycles to be inserted at the start of output of pixel data for each row or column |

| right_margin | HFP (Horizontal Front Porch ) | Number of pixel clocks between the end of each row or column of pixels and the LCD line clock output pulse |

| upper_margin | VBP (Vertical Back Porch) | Number of invalid lines at start of frame after vertical sync period |

| lower_margin | VFP (Vertical Front Porch) | The number of invalid lines from the end of the data output of the current frame to the start of the vertical synchronization period of the next frame |

| hsync_len | HPW (HSYNC plus width) |

Unit: pixel clock cycle also abbreviated as HWH (HSYNC width) in some manuals |

| vsync_len | VPW (VSYNC width) |

Unit: time to display a line Also abbreviated as VWH (VSYNC width) in some manuals |

| sync | No | FB_SYNC_HOR_HIGH_ACT (Horizontal sync active high) and FB_SYNC_VERT_HIGH_ACT (Vertical sync active high) can be set as needed |

| vmode | No | Most examples in the kernel are directly set to FB_VMODE_NONINTERLACED. Interlaced means interlaced scanning. In TV, a 2:1 interleaving rate is used, that is, each frame is divided into two fields, scanned twice vertically, one scans odd lines, and the other scans even lines. Obviously LCD is not this model. |

The content of this article is only a preliminary introduction. Many parameters are not introduced in detail. The LCD driver and support are relatively extensive. If you are interested, you can consult the relevant content online.