Brief Introduction About How to Work with SerDes on LS1046A Single Board Computer

The LS1046A is a cost-effective, power-efficient, and highly integrated system-on-chip(SoC) design that extends the reach of the NXP value-performance line of QorIQ communications processors. Featuring power-efficient 64-bit Arm ® Cortex ® -A72 cores with ECC-protected L1 and L2 cache memories for high reliability, running up to 1.8GHz.SerDes is a powerful but multiplexed module, here we'll take OK1046A-C single board computer to introduce how to work with SerDes.

1. How to configure SerDes

Users can configure SerDes by rigster

■ SerDes 1 Configuration:

- · Protocol(s): Selected using RCW[SRDS_PRTCL_S1]

- · PLLs: Enabled using RCW[SRDS_PLL_PD_S1]

- · PLL Reference Clock: RCW[SRDS_PLL_REF_CLK_SEL_S1]

- · (rates are determined by the protocol selection)

■ SerDes 2 Configuration:

- · Protocol(s): Selected using RCW[SRDS_PRTCL_S2]

- · PLLs: Enabled using RCW[SRDS_PLL_PD_S2]

- · PLL Reference Clock: RCW[SRDS_PLL_REF_CLK_SEL_S2]

- · Maximum rate: Selected using the following:

- · PCIe: RCW[SRDS_DIV_PEX_S2]

- · SATA rate selection is done in software

2. Protocol

■ SGMII notation for frame manager (FMan):

- · SGMII.n means SGMII (1 lane @ 1.25 Gbps or 3.125 Gbps)

- · "n" indicates which MAC on the FMan.

- · For example, "SGMII.9," indicates SGMII for MAC 9 on FMan.

■ QSGMII notation for frame manager (FMan):

- · "n" indicates which MAC on the FMan.

- · For example, "QSGMII.1,2,5,6," indicates QSGMII for MAC1, MAC2, MAC5

■ XFI notation for FMan:

- ·XFI.n means XFI (1 lane @ 10.3125 Gbps)

- ·"n" indicates which MAC on the FMan.

- ·For example, "XFI.9," indicates XFI for MAC 9 on FMan.

■ PCI Express:

- ·PCIen (8/5/2.5) means PCI express operating up to 8 or 5 or 2.5 Gbps depending on maximum rate selection and training.

- ·"n" indicates the nth PCIe

■ SATA:

·SATAn (6/3/1.5) means SATA operating at 6 or 3 or 1.5 Gbps depending on rate selection. The rate of selection is performed by PxSCTL[SPD] register as described in SATA 3.0.

In the first line of the above first table, there are configurable values for RCW[SRDS_PRTCL_S1/2], line D to line A are for four lanes of SerDes1/2, the last two lines are PLL of A/ B/ C/ D lanes. PCIe Gen1/2/3 can be configured by RCW[SRDS_DIV_PEX_Sn].

3. SerDes Protocol

Whether SerDes configuration is valid depends on below points:

PCIe. 1 can not be selected together on both SerDes1 and SerDes2.

When SRDS_PRTCL_S1 = 0x3333 and meanwhile SRDS_REFCLK_SEL_S1 is 0'b0, SerDes1 PLL1 should be disabled by SRDS_PLL_PD_S1

When SRDS_PRTCL_S2 = 0x8888 and meanwhile SRDS_REFCLK_SEL_S2 is 0'b0, SerDes2 PLL1 should be disabled by SRDS_PLL_PD_S2

4. Frame controller MAC

Each FMan can support 8x MAC which are available for various protocols as below

Note:

1) Half-duplex can not be supported by FMAN

2) MAC 1/ 5/ 6 10 are all used for QSGMII

5. SerDes clock

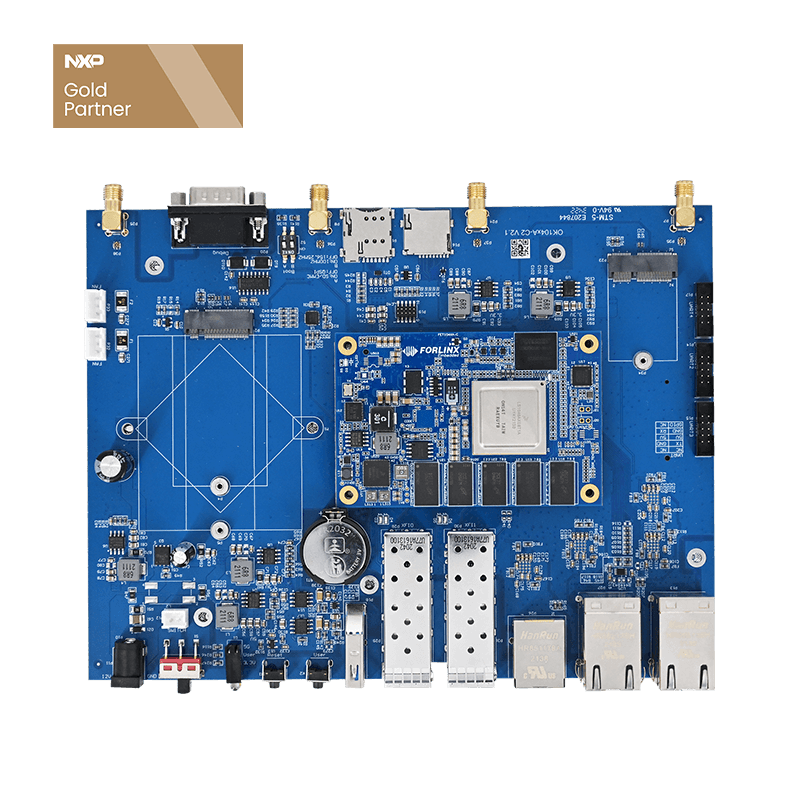

6. OK1046A-C related SerDes configuration

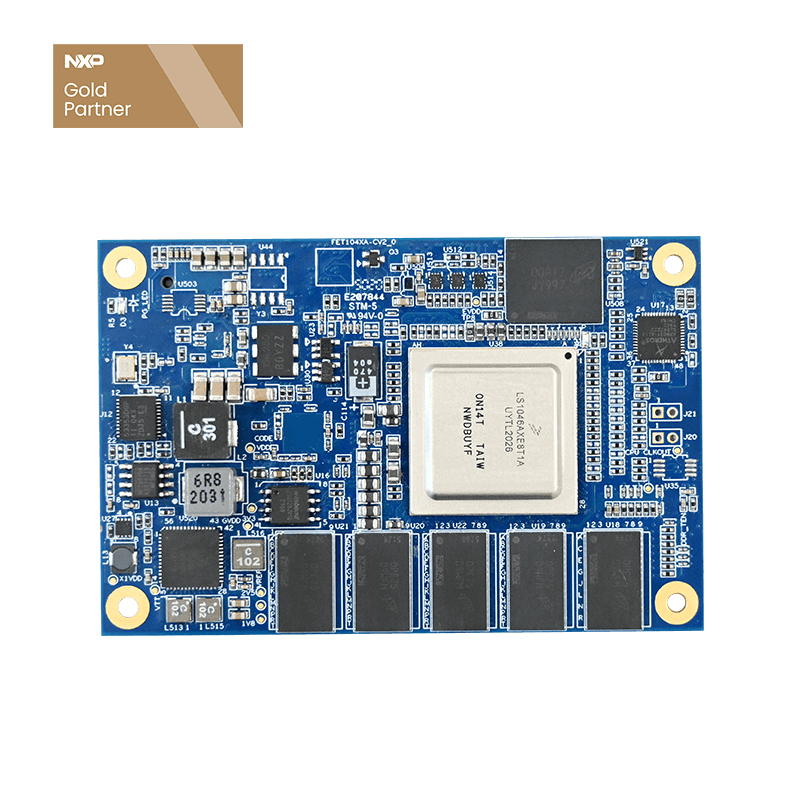

SerDes 1 of SoM FET1046A-C

SerDes 2 of SoM FET1046A-C

SerDes 1 of OK1046A-C carrier board

SerDes 2 of OK1046A-C carrier board

OK1046A-C is out of factory with configuration of 1014 for SerDes1 and 5559 for SerDes2. When designing carrier board, users can refer to Table31-1 and Table31-2 to configure SerDes1/ 2